# MC68HC05B4 MC68HC705B5 MC68HC05B6 MC68HC05B16 MC68HC705B16 MC68HC705B16N MC68HC705B32 MC68HC705B32

TECHNICAL DATA

# INTRODUCTION

- MODES OF OPERATION AND PIN DESCRIPTIONS

- MEMORY AND REGISTERS

- **INPUT/OUTPUT PORTS**

- PROGRAMMABLE TIMER

- SERIAL COMMUNICATIONS INTERFACE

- **PULSE LENGTH D/A CONVERTERS**

- ANALOG TO DIGITAL CONVERTER

- **RESETS AND INTERRUPTS**

- CPU CORE AND INSTRUCTION SET

- ELECTRICAL SPECIFICATIONS

- MECHANICAL DATA

- ORDERING INFORMATION

- APPENDICES

- HIGH SPEED OPERATION

15

INTRODUCTION

- MODES OF OPERATION AND PIN DESCRIPTIONS

- MEMORY AND REGISTERS

- **INPUT/OUTPUT PORTS**

- **PROGRAMMABLE TIMER**

- SERIAL COMMUNICATIONS INTERFACE

- **PULSE LENGTH D/A CONVERTERS**

- ANALOG TO DIGITAL CONVERTER

- **RESETS AND INTERRUPTS**

- **CPU CORE AND INSTRUCTION SET**

- ELECTRICAL SPECIFICATIONS

- **MECHANICAL DATA**

- ORDERING INFORMATION

- APPENDICES

- HIGH SPEED OPERATION

#### CUSTOMER FEEDBACK QUESTIONNAIRE (MC68HC05B6/D rev. 4)

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

1. How would you rate the quality of the document? Check one box in each category.

|     |                       | Excellent          |             | Poor        |                            | Exceller       | nt         |          | Poor    |           |    |

|-----|-----------------------|--------------------|-------------|-------------|----------------------------|----------------|------------|----------|---------|-----------|----|

|     | Organization          |                    |             |             | Tables                     |                |            |          |         |           |    |

|     | Readability           |                    |             |             | Table of contents          |                |            |          |         |           |    |

|     | Understandability     |                    |             |             | Index                      |                |            |          |         |           |    |

|     | Accuracy              |                    |             |             | Page size/binding          | g 🔲            |            |          |         |           |    |

|     | Illustrations         |                    |             |             | Overall impressio          | on 🔲           | E.         | H.       |         |           |    |

|     | Comments:             |                    |             |             |                            |                |            |          |         |           |    |

| 2.  | What is your interv   | ded use for this   | dooumon     | t) If more  | then one ention enalise    |                | 14 a.m. (1 | 0.0      |         |           |    |

| Ζ.  |                       |                    |             |             | than one option applies    |                | unenn (1   | , 2, 3). |         |           |    |

|     | Selection of device   | ior new applic     | allon       | ų           | Other De                   | ase specify: _ |            |          |         |           | -  |

|     | System design         |                    |             |             |                            |                |            |          |         |           | -  |

|     | Training purposes     |                    |             |             |                            |                |            |          |         |           | -  |

| 3.  | How well does this    | manual enable      | e you to pe | erform the  | task(s) outlined in ques   | tion 2?        |            |          |         |           |    |

|     |                       | Completely         | N           | lot at all  | Comments:                  |                |            |          |         |           |    |

|     |                       |                    |             |             |                            |                |            |          |         |           | _  |

| 4.  | How easy is it to fir | nd the informat    | ion you ar  | e looking f | or?                        |                |            |          |         |           |    |

|     |                       | Easy               | [           | Difficult   | Comments:                  |                |            |          |         |           | _  |

|     |                       |                    |             |             |                            |                |            |          |         |           |    |

| 5.  | Is the lovel of tech  | nical datail in th | o followin  | a soctions  | sufficient to allow you to | ounderstand    | now the    | dovice   | functio | 0002      |    |

| 5.  |                       |                    |             | y sections  | Sumplement to allow you to | Too little d   |            | uevice   |         | much deta | il |

|     | SECTION 1 INTR        | ODUCTION           |             |             |                            |                |            |          |         |           |    |

|     | SECTION 2 MOD         |                    |             | D PIN DES   | CRIPTIONS                  |                |            |          |         |           |    |

|     | SECTION 3 MEM         |                    |             |             |                            |                |            |          | H       |           |    |

|     | SECTION 4 INPU        | T/OUTPUT PC        | RTS         |             |                            |                |            |          | H       |           |    |

|     | SECTION 5 PRO         | GRAMMABLE -        | TIMER       |             |                            |                |            |          | H       |           |    |

|     | SECTION 6 SERI        | AL COMMUNI         | CATIONS     | INTERFAC    | Œ                          |                |            |          | H       |           |    |

|     | SECTION 7 PULS        | E LENGTH D/        | A CONVE     | RTERS       |                            |                |            |          | H       |           |    |

|     | SECTION 8 ANAL        | LOG TO DIGIT       | AL CONVE    | ERTER       |                            |                |            |          |         |           |    |

|     | SECTION 9 RESE        | ETS AND INTE       | RRUPTS      |             |                            |                |            |          | H       |           |    |

|     | SECTION 10 CPL        | J CORE AND I       | NSTRUCT     | TION SET    |                            |                |            |          | H       |           |    |

|     | SECTION 11 ELE        | CTRICAL SPE        | CIFICATI    | ONS         |                            |                |            |          | H       |           |    |

|     | SECTION 12 MEC        | CHANICAL DAT       | ΓA          |             |                            |                |            |          |         |           |    |

|     | SECTION 13 ORE        | DERING INFOF       | RMATION     |             |                            |                |            |          | H       |           |    |

|     | SECTION 14 APP        | 'ENDICES           |             |             |                            |                |            |          | H       |           |    |

|     | SECTION 15 HIG        | H SPEED OPE        | RATION      |             |                            |                |            |          | H.      |           |    |

| Cor | nments:               |                    |             |             |                            |                |            | -        | -       | -         |    |

| 6.  | Have you found any    | y errors? If so,   | please co   | mment:      |                            |                |            |          |         |           | -  |

|     |                       |                    |             |             |                            |                |            |          |         |           | _  |

| 7.  | From your point of    | view, is anythin   | g missing   | from the d  | ocument? If so, please     | say what:      |            |          |         |           | _  |

| How could we improve this document                                         | l?                                                                                     |                                 |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------|

| How would you rate Motorola's docur                                        | nentation?                                                                             | <br> <br>                       |

|                                                                            | Excellent Poor                                                                         | 1                               |

| <ul> <li>In general</li> <li>Against other semiconductor suppli</li> </ul> |                                                                                        |                                 |

| Which semiconductor manufacturer p<br>Which company (in any field) provide | provides the best technical documentation?                                             | 1                               |

| How many years have you worked wi                                          |                                                                                        |                                 |

| Less than 1 year 1-3 years                                                 | 3–5 years More than 5 years                                                            | 1                               |

|                                                                            | – Second fold back along this line –                                                   |                                 |

|                                                                            |                                                                                        | <br> <br>                       |

| By air mail                                                                | NE PAS AFFRANCHIR                                                                      | 1                               |

| Par avion                                                                  |                                                                                        | 1                               |

| BRS NUMBER PHQ-B/207/G                                                     |                                                                                        | 1                               |

| CCRI NUMERO PHQ-B/207/G                                                    | NO STAMP REQUIRED                                                                      | - <u>-</u>                      |

|                                                                            |                                                                                        | st fo                           |

|                                                                            |                                                                                        | First fold back along this line |

|                                                                            | REPONSE PAYEE                                                                          | ick a                           |

|                                                                            | GRANDE-BRETAGNE                                                                        | long                            |

|                                                                            |                                                                                        | this                            |

|                                                                            | Motorola Ltd.,<br>Colvilles Road,                                                      | line -                          |

|                                                                            | Kelvin Industrial Estate,                                                              | 1                               |

|                                                                            | EAST KILBRIDE,<br>G75 8BR.                                                             | 1                               |

|                                                                            | GREAT BRITAIN.                                                                         |                                 |

| Semiconductor Products Sec                                                 | ctor F.A.O. Technical Publications Manager                                             | 1                               |

| Semiconductor Products Sec                                                 | (re: MC68HC05B6/D rev. 4)                                                              | 1                               |

|                                                                            | – Third fold back along this line –                                                    |                                 |

|                                                                            | the semiconductor industry regarding a move towards providing data sheets in ele       | ectronic                        |

| form. If you have any opinion on this s                                    | subject, please comment.                                                               |                                 |

| We would be grateful if you would sup<br>Name:                             | pply the following information (at your discretion), or attach your card.<br>Phone No: | 1                               |

| Position                                                                   | FAX No:                                                                                | 1                               |

| Department:                                                                |                                                                                        | 1                               |

| Company:                                                                   |                                                                                        | 1                               |

| Address:                                                                   |                                                                                        | 1                               |

| Thank you for helping us improve our                                       | r documentation                                                                        | 1                               |

| Graham Forbes, Technical Publication                                       |                                                                                        | 1                               |

|                                                                            |                                                                                        | 1                               |

|                                                                            | <ul> <li>Finally, tuck this edge into opposite flap –</li> </ul>                       |                                 |

Į.

# MC68HC05B6

# High-density Complementary Metal Oxide Semiconductor (HCMOS) Microcomputer Unit

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use. even if such claim alleges that Motorola and the design or manufacture of the part. Motorola and \*\* are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

# Conventions

Where abbreviations are used in the text, an explanation can be found in the glossary, at the back of this manual. Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, shaded cells in a register diagram indicate that the bit is either unused or reserved; 'u' is used to indicate an undefined state (on reset).

Unless otherwise stated, pins labelled "NU" should be tied to  $V_{SS}$  in an electrically noisy environment. Pins labelled "NC" can be left floating, since they are not bonded to any part of the device.

# **TABLE OF CONTENTS**

Paragraph Number

TITLE

Page Number

#### 1 INTRODUCTION

| 1.1 | Features                        | 1- | -2 |

|-----|---------------------------------|----|----|

| 1.2 | Mask options for the MC68HC05B6 | 1- | -3 |

#### 2 MODES OF OPERATION AND PIN DESCRIPTIONS

| 2.1     | Modes of operation                 | 2–1  |

|---------|------------------------------------|------|

| 2.1.1   | Single chip mode                   | 2–1  |

| 2.2     | Serial RAM loader                  | 2–2  |

| 2.3     | 'Jump to any address'              | 2–4  |

| 2.4     | Low power modes                    | 2–6  |

| 2.4.1   | STOP                               |      |

| 2.4.2   | WAIT                               | 2–8  |

| 2.4.2.1 | Power consumption during WAIT mode | 2–8  |

| 2.4.3   | SLOW mode                          | 2–9  |

| 2.4.3.1 | Miscellaneous register             | 2–9  |

| 2.5     | Pin descriptions                   | 2–10 |

| 2.5.1   | VDD and VSS                        | 2–10 |

| 2.5.2   | IRQ                                | 2–10 |

| 2.5.3   | RESET                              | 2–10 |

| 2.5.4   | TCAP1                              | 2–10 |

| 2.5.5   | TCAP2                              | 2–11 |

| 2.5.6   | TCMP1                              | 2–11 |

| 2.5.7   | TCMP2                              | 2–11 |

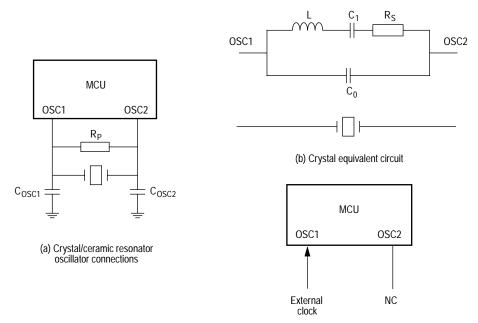

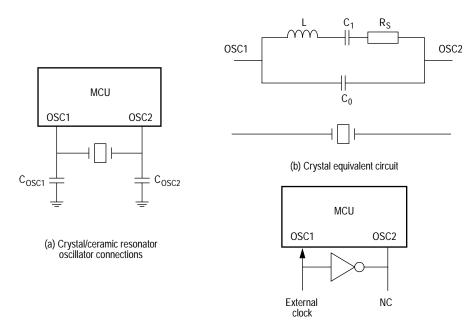

| 2.5.8   | OSC1, OSC2                         | 2–11 |

| 2.5.8.1 | Crystal                            | 2–11 |

| 2.5.8.2 | 2 Ceramic resonator                | 2–11 |

| 2.5.8.3 | B External clock                   | 2–12 |

| 2.5.9   | RDI (Receive data in)              | 2–13 |

| 2.5.10  | TDO (Transmit data out)            | 2–13 |

| 2.5.11  | SCLK                               | 2–13 |

| 2.5.12  | PLMA                               | 2–13 |

#### TABLE OF CONTENTS

Page Number

| 2.5.13 | PLMB                          |      |

|--------|-------------------------------|------|

|        | VPP1                          |      |

| 2.5.15 | VRH                           | 2–13 |

|        | VRL                           |      |

|        | PA0 – PA7/PB0 – PB7/PC0 – PC7 |      |

| 2.5.18 | PD0/AN0–PD7/AN7               | 2–13 |

|        |                               |      |

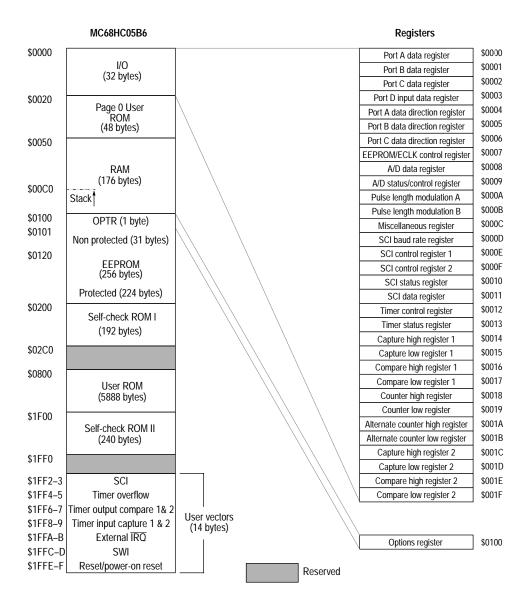

### 3 MEMORY AND REGISTERS

| 3.1   | Registers                    | .3–1 |

|-------|------------------------------|------|

| 3.2   | RAM                          | .3–1 |

| 3.3   | ROM                          | .3–1 |

| 3.4   | Self-check ROM               | .3–2 |

| 3.5   | EEPROM                       | .3–3 |

| 3.5.1 | EEPROM control register      | .3–3 |

| 3.5.2 | EEPROM read operation        | .3–5 |

| 3.5.3 | EEPROM erase operation       | .3–5 |

| 3.5.4 | EEPROM programming operation | .3–6 |

| 3.5.5 | Options register (OPTR)      | .3–6 |

| 3.6   | EEPROM during STOP mode      |      |

| 3.7   | EEPROM during WAIT mode      | .3–7 |

| 3.8   | Miscellaneous register       | .3–9 |

### 4 INPUT/OUTPUT PORTS

| 4.1     | Input/output programming                       | 4–1 |

|---------|------------------------------------------------|-----|

| 4.2     | Ports A and B                                  | 4–2 |

| 4.3     | Port C                                         | 4–3 |

| 4.4     | Port D                                         | 4–3 |

| 4.5     | Port registers                                 | 4–4 |

| 4.5.1   | Port data registers A and B (PORTA and PORTB)  | 4–4 |

| 4.5.2   | Port data register C (PORTC)                   | 4–4 |

| 4.5.3   | Port data register D (PORTD)                   | 4–5 |

| 4.5.3.1 | A/D status/control register                    | 4–5 |

| 4.5.4   | Data direction registers (DDRA, DDRB and DDRC) | 4–5 |

| 4.6     | Other port considerations                      |     |

#### TABLE OF CONTENTS

#### 5 PROGRAMMABLE TIMER

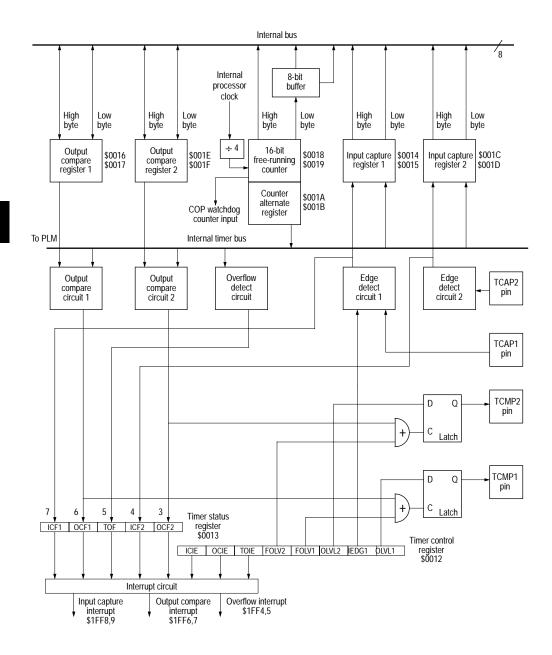

| 5.1   | Counter                                               | 5–1  |

|-------|-------------------------------------------------------|------|

| 5.1.1 | Counter register and alternate counter register       | 5–3  |

| 5.2   | Timer control and status                              | 5–4  |

| 5.2.1 | Timer control register (TCR)                          | 5–4  |

| 5.2.2 | Timer status register (TSR)                           | 5–6  |

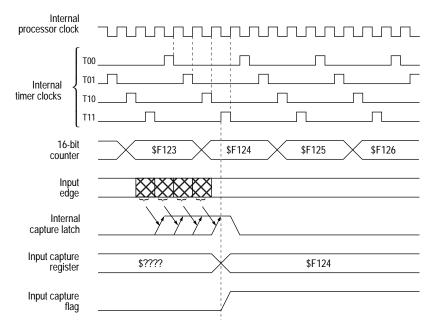

| 5.3   | Input capture                                         | 5–7  |

| 5.3.1 | Input capture register 1 (ICR1)                       | 5–7  |

| 5.3.2 | Input capture register 2 (ICR2)                       | 5–8  |

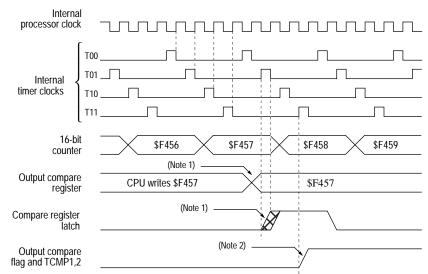

| 5.4   | Output compare                                        | 5–9  |

| 5.4.1 | Output compare register 1 (OCR1)                      | 5–9  |

| 5.4.2 | Output compare register 2 (OCR2)                      | 5–10 |

| 5.4.3 | Software force compare                                | 5–11 |

| 5.5   | Pulse Length Modulation (PLM)                         | 5–11 |

| 5.5.1 | Pulse length modulation registers A and B (PLMA/PLMB) | 5–11 |

| 5.6   | Timer during STOP mode                                | 5–12 |

| 5.7   | Timer during WAIT mode                                | 5–12 |

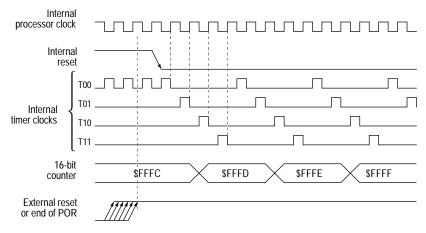

| 5.8   | Timer state diagrams                                  | 5–12 |

|       |                                                       |      |

### 6 SERIAL COMMUNICATIONS INTERFACE

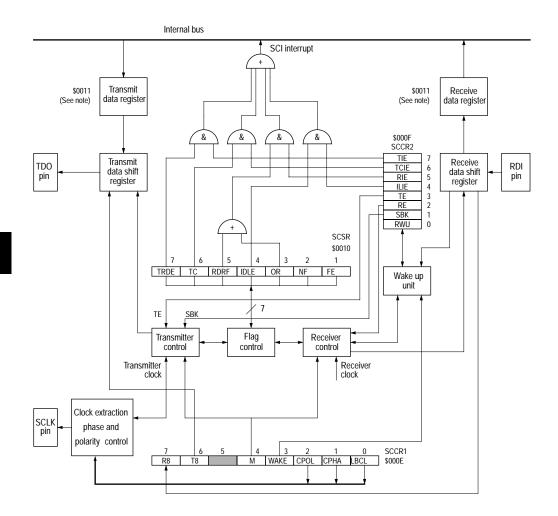

| 6.1    | SCI two-wire system features                     | 6–1  |

|--------|--------------------------------------------------|------|

| 6.2    | SCI receiver features                            | 6–3  |

| 6.3    | SCI transmitter features                         | 6–3  |

| 6.4    | Functional description                           | 6–3  |

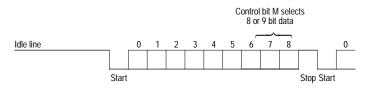

| 6.5    | Data format                                      | 6–5  |

| 6.6    | Receiver wake-up operation                       | 6–5  |

| 6.6.1  | Idle line wake-up                                | 6–6  |

| 6.6.2  | Address mark wake-up                             | 6–6  |

| 6.7    | Receive data in (RDI)                            | 6–6  |

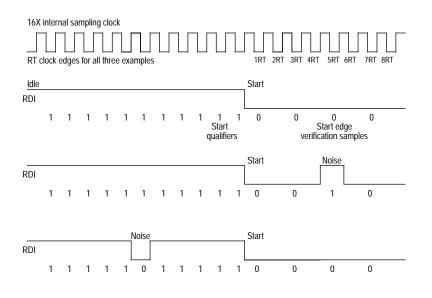

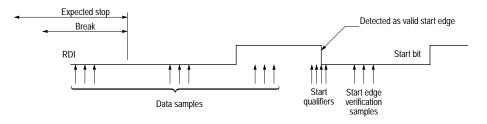

| 6.8    | Start bit detection                              | 6–6  |

| 6.9    | Transmit data out (TDO)                          |      |

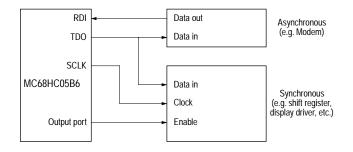

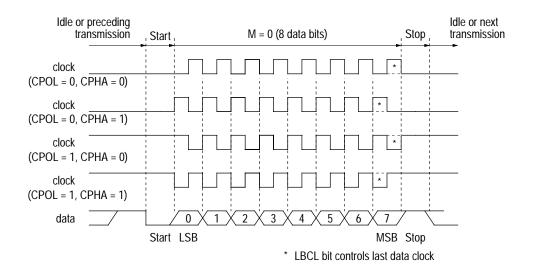

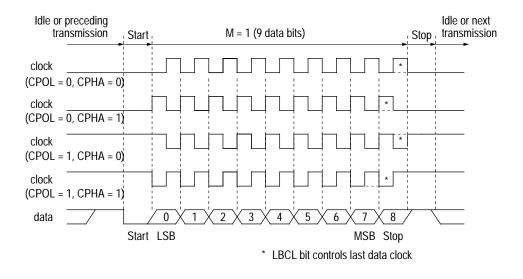

| 6.10   | SCI synchronous transmission                     |      |

| 6.11   | SCI registers                                    | 6–10 |

| 6.11.1 | Serial communications data register (SCDR)       | 6–10 |

| 6.11.2 | Serial communications control register 1 (SCCR1) | 6–10 |

| 6.11.3 | Serial communications control register 2 (SCCR2) | 6–14 |

| 6.11.4 | Serial communications status register (SCSR)     | 6–16 |

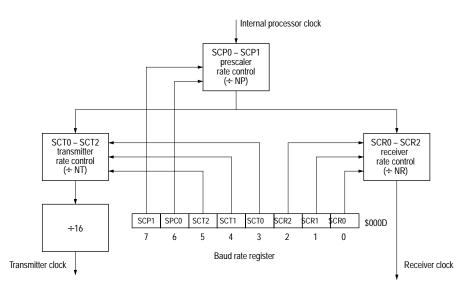

| 6.11.5 | Baud rate register (BAUD)                        | 6–18 |

| 6.12   | Baud rate selection                              | 6–19 |

| 6.13   | SCI during STOP mode                             |      |

| 6.14   | SCI during WAIT mode                             | 6–21 |

#### TABLE OF CONTENTS

#### 7 PULSE LENGTH D/A CONVERTERS

| 7.1 | Miscellaneous register | 7–3 |

|-----|------------------------|-----|

|     | PLM clock selection    |     |

|     | PLM during STOP mode   |     |

| 7.4 | PLM during WAIT mode   | 7–4 |

|     |                        |     |

#### 8

# ANALOG TO DIGITAL CONVERTER

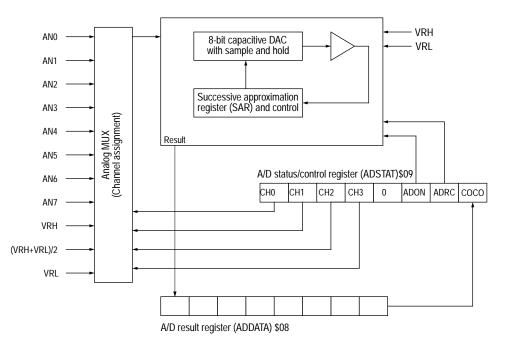

| A/D converter operation              | 8–1                                                                                                                                            |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                                                                                                                                |

| Port D data register (PORTD)         |                                                                                                                                                |

| A/D result data register (ADDATA)    | 8–3                                                                                                                                            |

| A/D status/control register (ADSTAT) |                                                                                                                                                |

| A/D converter during STOP mode       | 8–6                                                                                                                                            |

| A/D converter during WAIT mode       | 8–6                                                                                                                                            |

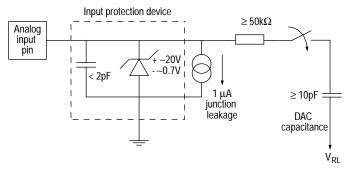

| Port D analog input                  | 8–6                                                                                                                                            |

|                                      | A/D result data register (ADDATA)<br>A/D status/control register (ADSTAT)<br>A/D converter during STOP mode<br>A/D converter during WAIT mode. |

### 9 RESETS AND INTERRUPTS

| 9.1     | Resets                                           | 9–1 |

|---------|--------------------------------------------------|-----|

| 9.1.1   | Power-on reset                                   |     |

| 9.1.2   | Miscellaneous register                           |     |

| 9.1.3   | RESET pin                                        |     |

| 9.1.4   | Computer operating properly (COP) watchdog reset |     |

| 9.1.4.1 | COP watchdog during STOP mode                    |     |

| 9.1.4.2 | COP watchdog during WAIT mode                    |     |

| 9.1.5   | Functions affected by reset                      |     |

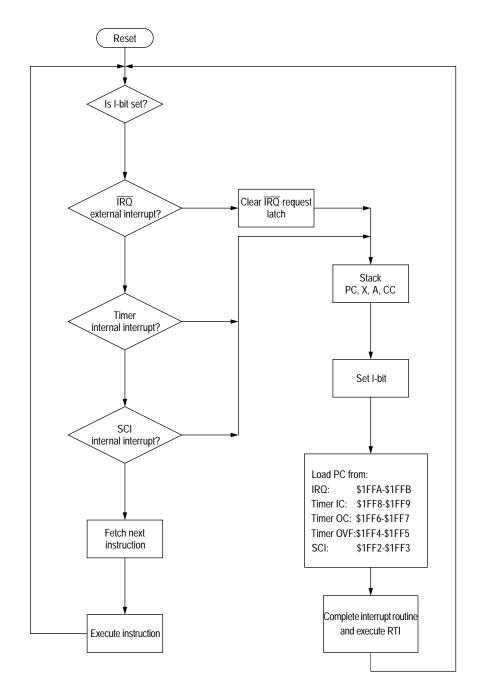

| 9.2     | Interrupts                                       |     |

| 9.2.1   | Interrupt priorities                             |     |

| 9.2.2   | Nonmaskable software interrupt (SWI)             |     |

| 9.2.3   | Maskable hardware interrupts                     |     |

| 9.2.3.1 | External interrupt (IRQ)                         |     |

| 9.2.3.2 | Miscellaneous register                           | 9–9 |

| 9.2.3.3 | Timer interrupts                                 |     |

| 9.2.3.4 | Serial communications interface (SCI) interrupts |     |

| 9.2.4   | Hardware controlled interrupt sequence           |     |

#### TABLE OF CONTENTS

#### 10

### **CPU CORE AND INSTRUCTION SET**

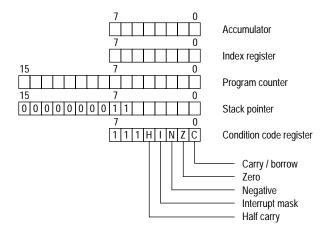

| 10.1   | Registers                      | 10–1  |

|--------|--------------------------------|-------|

| 10.1.1 | Accumulator (A)                |       |

| 10.1.2 | Index register (X)             |       |

| 10.1.3 | Program counter (PC)           | 10–2  |

| 10.1.4 | Stack pointer (SP)             |       |

| 10.1.5 | Condition code register (CCR)  | 10–2  |

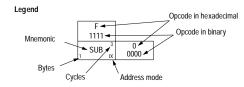

| 10.2   | Instruction set                | 10–3  |

| 10.2.1 | Register/memory Instructions   | 10–4  |

| 10.2.2 | Branch instructions            | 10–4  |

| 10.2.3 | Bit manipulation instructions  | 10–4  |

| 10.2.4 | Read/modify/write instructions | 10–4  |

| 10.2.5 | Control instructions           | 10–4  |

| 10.2.6 | Tables                         | 10–4  |

| 10.3   | Addressing modes               | 10–11 |

| 10.3.1 | Inherent                       | 10–11 |

| 10.3.2 | Immediate                      | 10–11 |

| 10.3.3 | Direct                         | 10–11 |

| 10.3.4 | Extended                       | 10–12 |

| 10.3.5 | Indexed, no offset             | 10–12 |

| 10.3.6 | Indexed, 8-bit offset          | 10–12 |

| 10.3.7 | Indexed, 16-bit offset         | 10–12 |

| 10.3.8 | Relative                       | 10–13 |

| 10.3.9 | Bit set/clear                  | 10–13 |

| 10.3.1 | 0 Bit test and branch          | 10–13 |

#### 11

# **ELECTRICAL SPECIFICATIONS**

| 11.1   | Absolute maximum ratings                  | 11–1  |

|--------|-------------------------------------------|-------|

|        | DC electrical characteristics             |       |

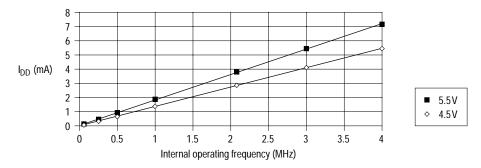

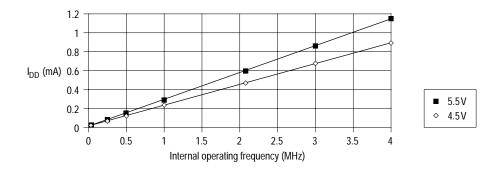

| 11.2.1 | I <sub>DD</sub> trends for 5V operation   | 11–3  |

| 11.2.2 | I <sub>DD</sub> trends for 3.3V operation | 11–6  |

| 11.3   | A/D converter characteristics             | 11–8  |

| 11.4   | Control timing                            | 11–10 |

## 12

# MECHANICAL DATA

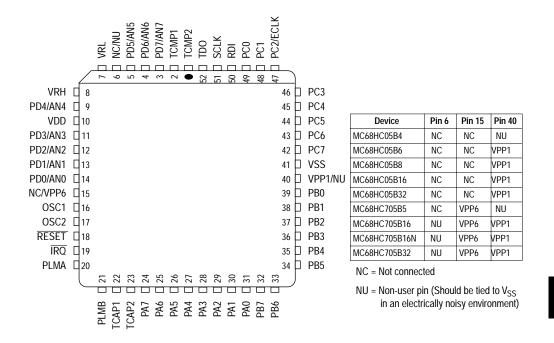

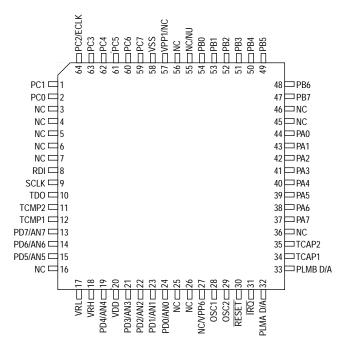

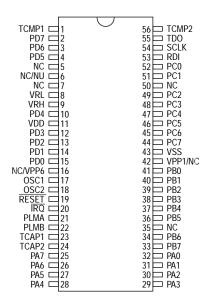

| 12.1   | MC68HC05B family pin configurations12-1       | 1 |

|--------|-----------------------------------------------|---|

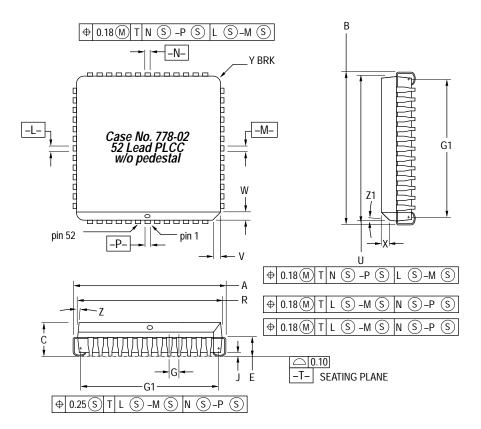

|        | 52-pin plastic leaded chip carrier (PLCC)12-1 |   |

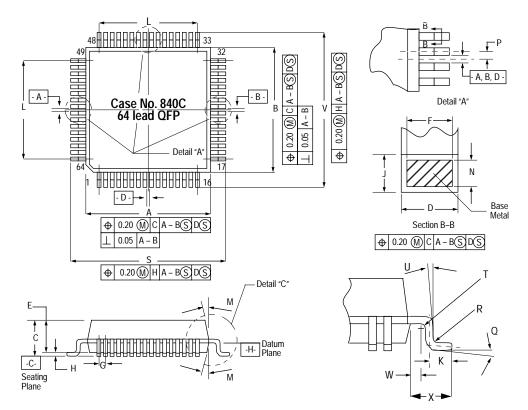

| 12.1.2 | 64-pin quad flat pack (QFP)12-2               | 2 |

#### TABLE OF CONTENTS

Page Number

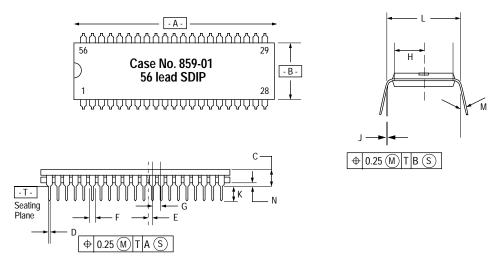

| 12.1.3 | 56-pin shrink dual in line package (SDIP) |  |

|--------|-------------------------------------------|--|

| 12.2   | MC68HC05B6 mechanical dimensions          |  |

| 12.2.1 | 52-pin plastic leaded chip carrier (PLCC) |  |

| 12.2.2 | 64-pin quad flat pack (QFP)               |  |

| 12.2.3 | 56-pin shrink dual in line package (SDIP) |  |

### 13 ORDERING INFORMATION

| 13.1 | EPROMS                       | 13–2 |

|------|------------------------------|------|

| 13.2 | Verification media           | 13–2 |

| 13.3 | ROM verification units (RVU) | 13–2 |

#### A MC68HC05B4

| A.1 | Features        | A–1 |

|-----|-----------------|-----|

|     | Self-check mode |     |

# В

# MC68HC05B8

| B.1 | Features | B– | ·1 |

|-----|----------|----|----|

|-----|----------|----|----|

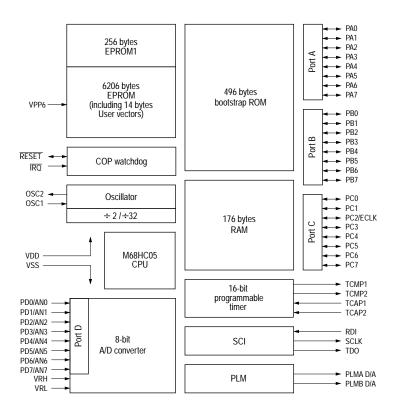

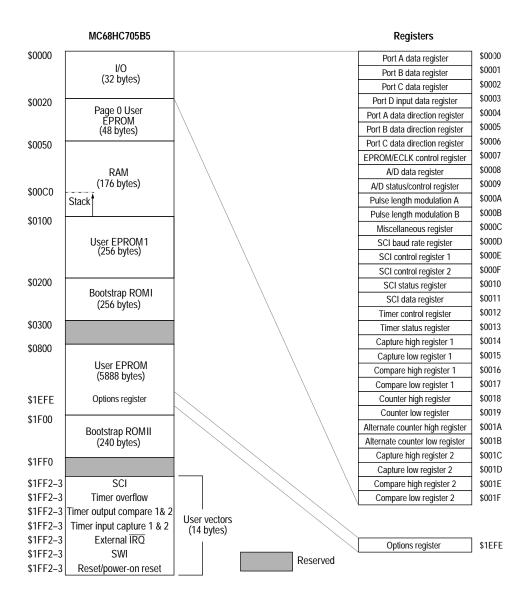

### C MC68HC705B5

| C.1   | Features                                      | C–1  |

|-------|-----------------------------------------------|------|

| C.2   | EPROM                                         | C–5  |

| C.2.1 | EPROM programming operation                   | C–5  |

| C.3   | EPROM registers                               |      |

| C.3.1 | EPROM control register                        | C–6  |

| C.4   | Options register (OPTR)                       | C–7  |

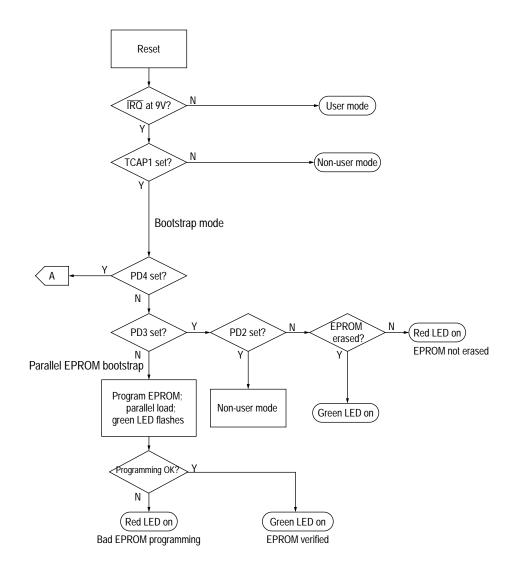

| C.5   | Bootstrap mode                                | C–8  |

| C.5.1 | Erased EPROM verification                     | C–11 |

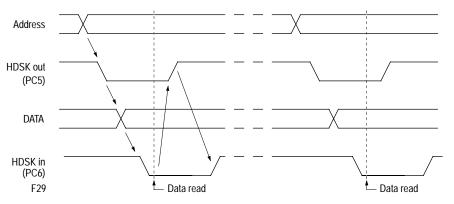

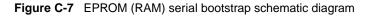

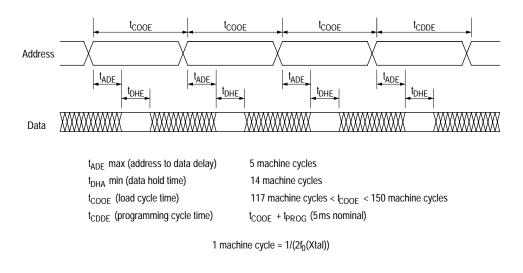

| C.5.2 | EPROM parallel bootstrap load                 | C–11 |

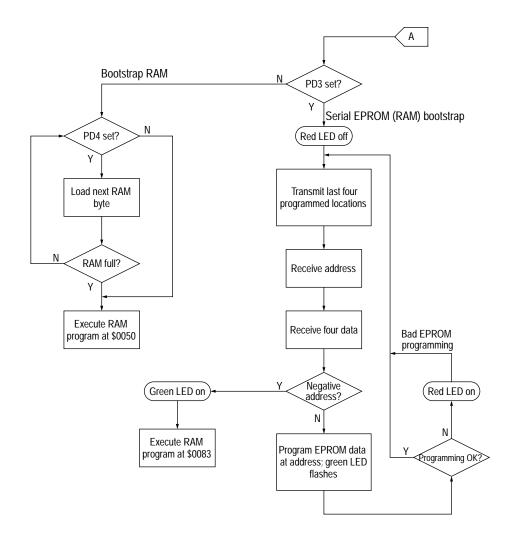

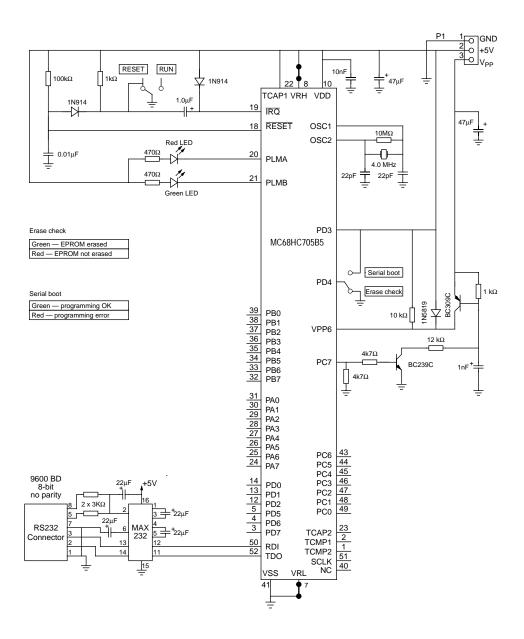

| C.5.3 | EPROM (RAM) serial bootstrap load and execute | C–13 |

| C.5.4 | RAM parallel bootstrap load and execute       |      |

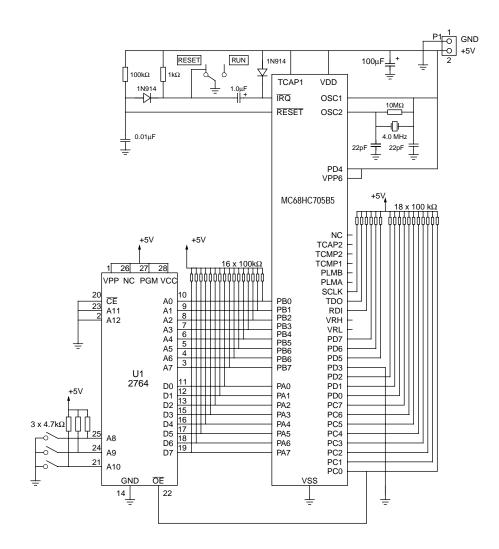

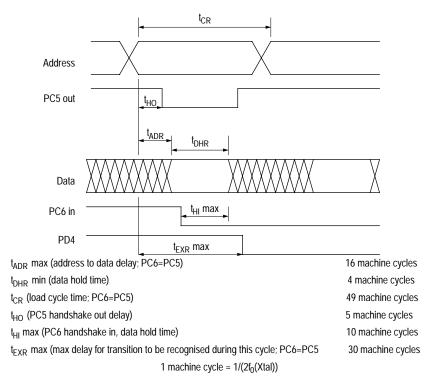

| C.5.5 | Bootstrap loader timing diagrams              | C–17 |

| C.6   | DC electrical characteristics                 | C–19 |

| C.7   | Control timing                                | C–19 |

#### TABLE OF CONTENTS

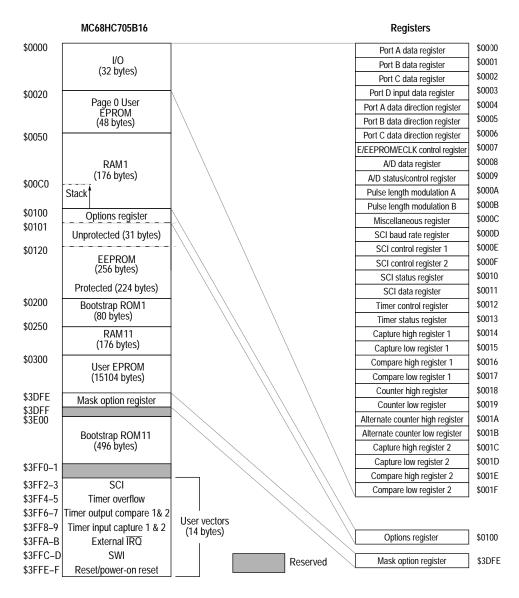

### D MC68HC05B16

| D.1 | Features            | .D–1 |

|-----|---------------------|------|

| D.2 | Self-check routines | D–2  |

| D.3 | External clock      | .D–4 |

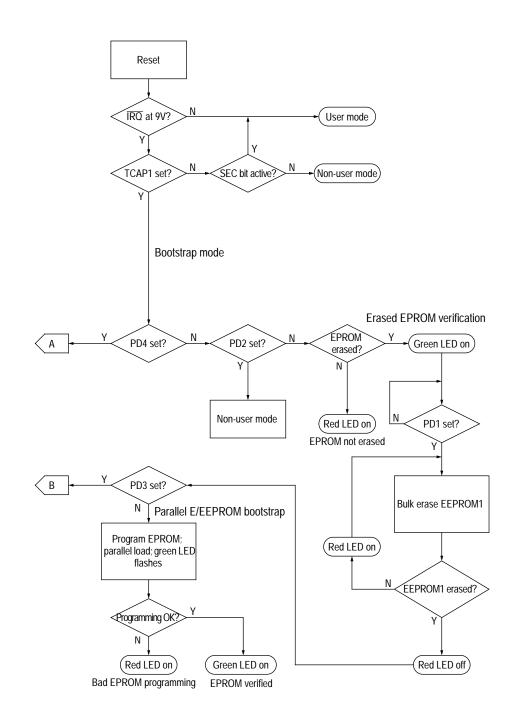

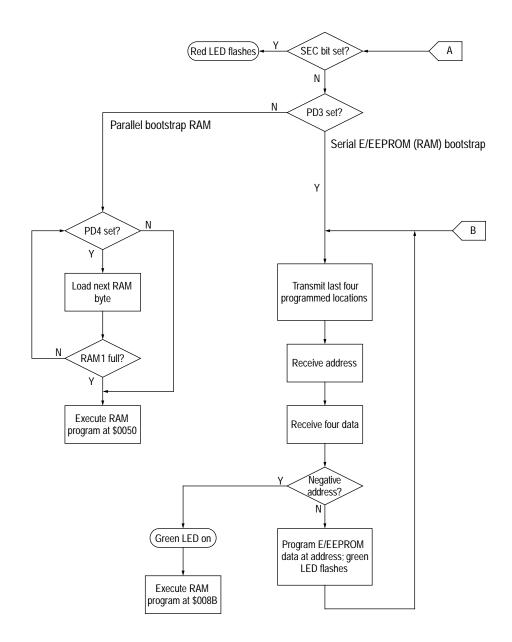

#### E MC68HC705B16

| E.1     | Features                           | E–2  |

|---------|------------------------------------|------|

| E.2     | External clock                     | E–5  |

| E.3     | EPROM                              | E–5  |

| E.3.1   | EPROM read operation               | E–5  |

| E.3.2   | EPROM program operation            | E–5  |

| E.3.3   | EPROM/EEPROM/ECLK control register | E–6  |

| E.3.4   | Mask option register               | E–8  |

| E.3.5   | EEPROM options register (OPTR)     | E–9  |

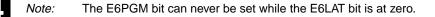

| E.4     | Bootstrap mode                     | E–10 |

| E.4.1   | Erased EPROM verification          | E–13 |

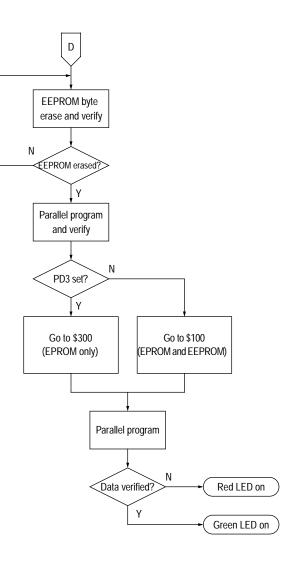

| E.4.2   | EPROM/EEPROM parallel bootstrap    | E–13 |

| E.4.3   | EEPROM/EPROM/RAM serial bootstrap  | E–16 |

| E.4.4   | RAM parallel bootstrap             | E–19 |

| E.4.4.1 | 1 Jump to start of RAM (\$0050)    | E–20 |

| E.5     | Absolute maximum ratings           | E–21 |

| E.6     | DC electrical characteristics      | E–22 |

| E.7     | A/D converter characteristics      | E–24 |

| E.8     | Control timing                     | E–26 |

| E.9     | EPROM electrical characteristics   |      |

# F

# MC68HC705B16N

| F.1   | Features                           | F–2  |

|-------|------------------------------------|------|

| F.2   | External clock                     | F–5  |

| F.3   | RESET pin                          | F–5  |

| F.4   | EPROM                              | F–5  |

| F.4.1 | EPROM read operation               | F–5  |

| F.4.2 | EPROM program operation            | F–6  |

| F.4.3 | EPROM/EEPROM/ECLK control register | F–6  |

| F.4.4 | Mask option register               | F–8  |

| F.4.5 | EEPROM options register (OPTR)     | F–9  |

| F.5   | Bootstrap mode                     | F–10 |

| F.5.1 | Erased EPROM verification          | F–13 |

#### TABLE OF CONTENTS

Page Number

| F.5.2   | EPROM/EEPROM parallel bootstrap  | F–13 |

|---------|----------------------------------|------|

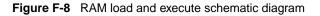

| F.5.3   | Serial RAM loader                | F–16 |

| F.5.3.1 | Jump to start of RAM (\$0051)    | F–16 |

| F.6     | Absolute maximum ratings         | F–19 |

| F.7     | DC electrical characteristics    | F–20 |

| F.8     | A/D converter characteristics    | F–22 |

| F.9     | Control timing                   | F–24 |

| F.10    | EPROM electrical characteristics | F–26 |

# G

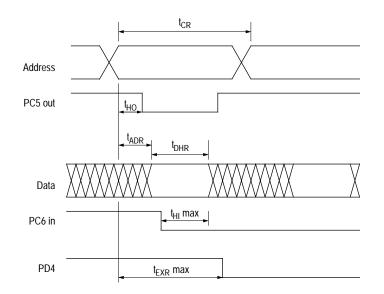

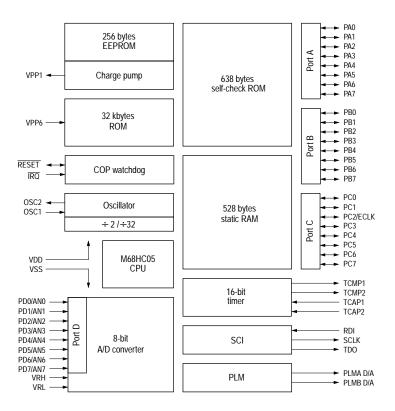

# MC68HC05B32

| G.1 | Features       | G– | ·1 |

|-----|----------------|----|----|

|     | External clock |    |    |

#### H MC68HC705B32

| Features                         | Н_3                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                               |

| RESET pin                        | H–7                                                                                                                                                                                                                                                                                                                                                                                           |

| EPROM                            | H–7                                                                                                                                                                                                                                                                                                                                                                                           |

| EPROM read operation             | H–8                                                                                                                                                                                                                                                                                                                                                                                           |

| EPROM program operation          | H–8                                                                                                                                                                                                                                                                                                                                                                                           |

| EPROM/EEPROM control register    |                                                                                                                                                                                                                                                                                                                                                                                               |

| Mask option register             | H–11                                                                                                                                                                                                                                                                                                                                                                                          |

| Options register (OPTR)          | H–12                                                                                                                                                                                                                                                                                                                                                                                          |

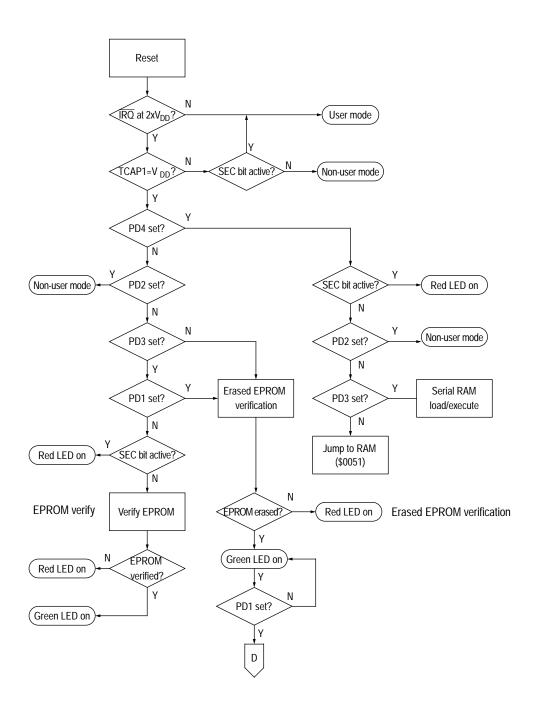

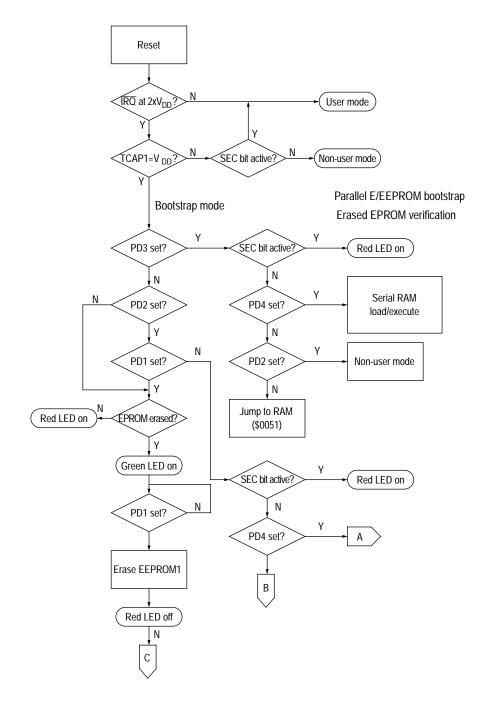

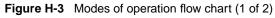

| Bootstrap mode                   | H–13                                                                                                                                                                                                                                                                                                                                                                                          |

| Erased EPROM verification        | H–16                                                                                                                                                                                                                                                                                                                                                                                          |

| EPROM/EEPROM parallel bootstrap  | H–16                                                                                                                                                                                                                                                                                                                                                                                          |

| Serial RAM loader                | H–19                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 Jump to start of RAM (\$0051)  | H–19                                                                                                                                                                                                                                                                                                                                                                                          |

| Absolute maximum ratings         | H–22                                                                                                                                                                                                                                                                                                                                                                                          |

| DC electrical characteristics    | H–23                                                                                                                                                                                                                                                                                                                                                                                          |

| A/D converter characteristics    | H–25                                                                                                                                                                                                                                                                                                                                                                                          |

| Control timing                   | H–27                                                                                                                                                                                                                                                                                                                                                                                          |

| EPROM electrical characteristics | H–29                                                                                                                                                                                                                                                                                                                                                                                          |

|                                  | EPROM read operation<br>EPROM program operation<br>EPROM/EEPROM control register<br>Mask option register<br>Options register (OPTR)<br>Bootstrap mode<br>Erased EPROM verification<br>EPROM/EEPROM parallel bootstrap<br>Serial RAM loader<br>1 Jump to start of RAM (\$0051)<br>Absolute maximum ratings<br>DC electrical characteristics<br>A/D converter characteristics<br>Control timing |

#### L

# HIGH SPEED OPERATION

| l.1 | DC electrical characteristics   | I–2 |

|-----|---------------------------------|-----|

| 1.2 | A/D converter characteristics   | I–3 |

| 1.3 | Control timing for 5V operation | I–4 |

# **LIST OF FIGURES**

| Figure<br>Number | TITLE                                                          | Page<br>Number |

|------------------|----------------------------------------------------------------|----------------|

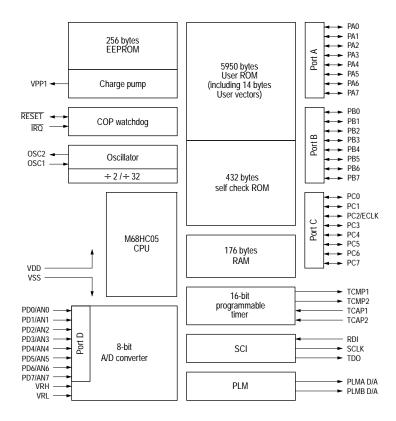

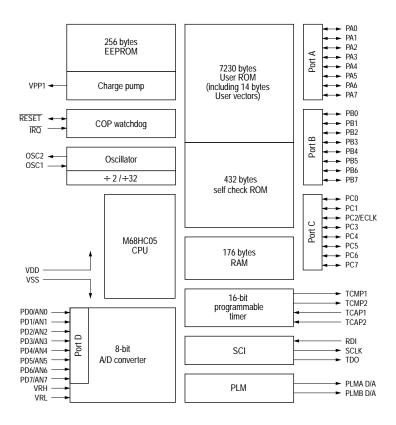

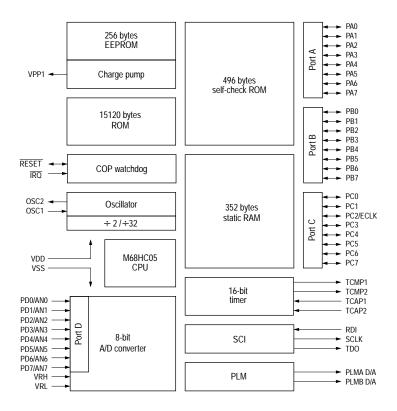

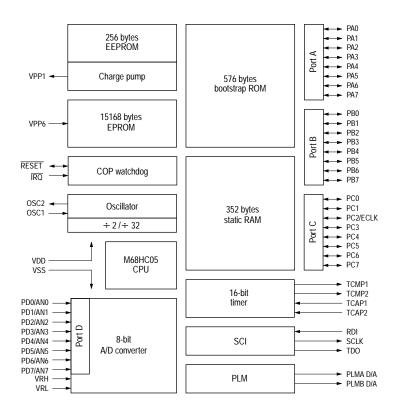

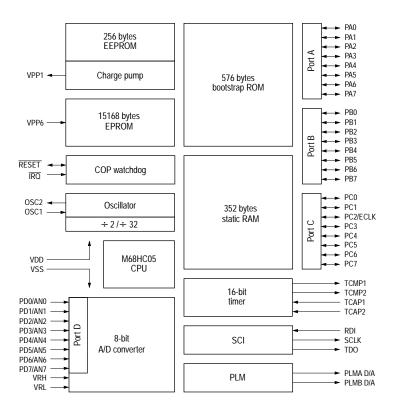

| 1-1              | MC68HC05B6 block diagram                                       | 1–3            |

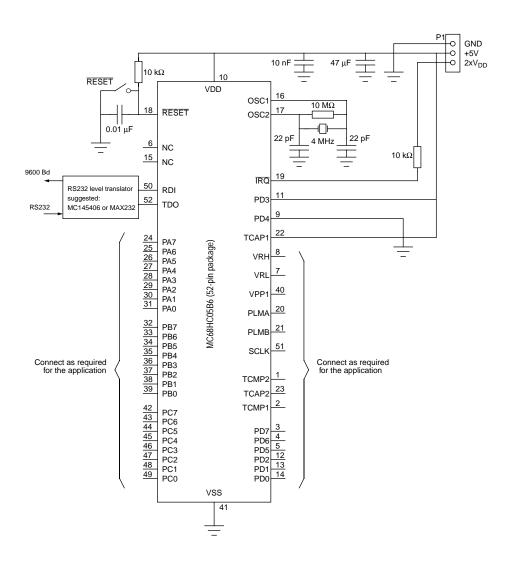

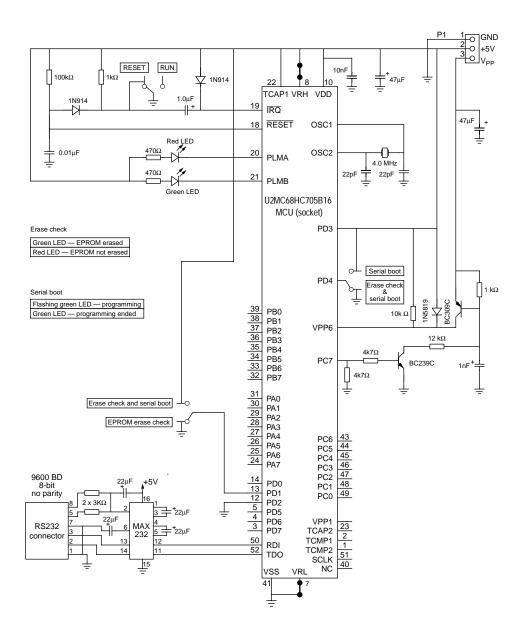

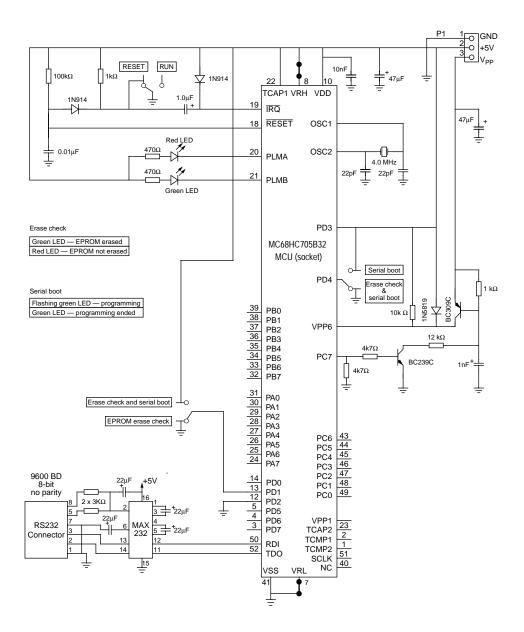

| 2-1              | MC68HC05B6 'load program in RAM and execute' schematic diagram | 2–3            |

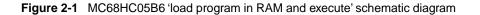

| 2-2              | MC68HC05B6 'jump to any address' schematic diagram             | 2–5            |

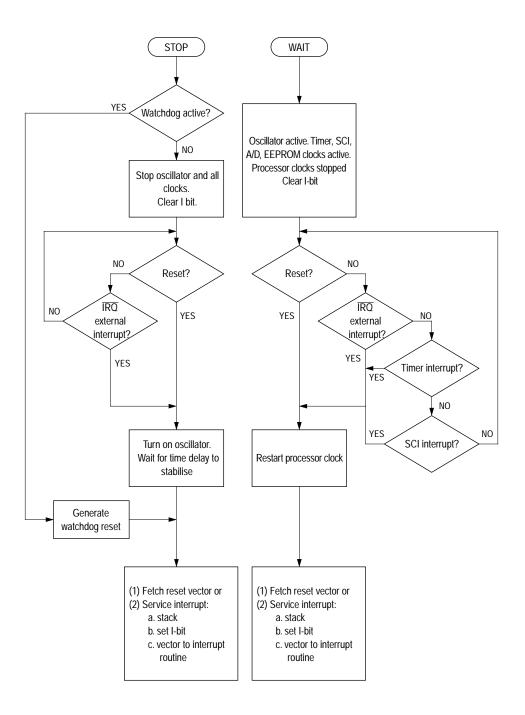

| 2-3              | STOP and WAIT flowcharts                                       | 2–7            |

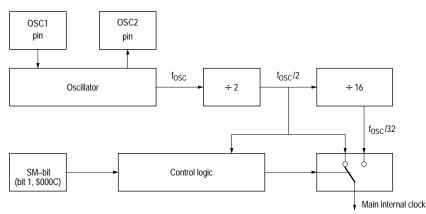

| 2-4              | Slow mode divider block diagram                                | 2–9            |

| 2-5              | Oscillator connections                                         | 2–12           |

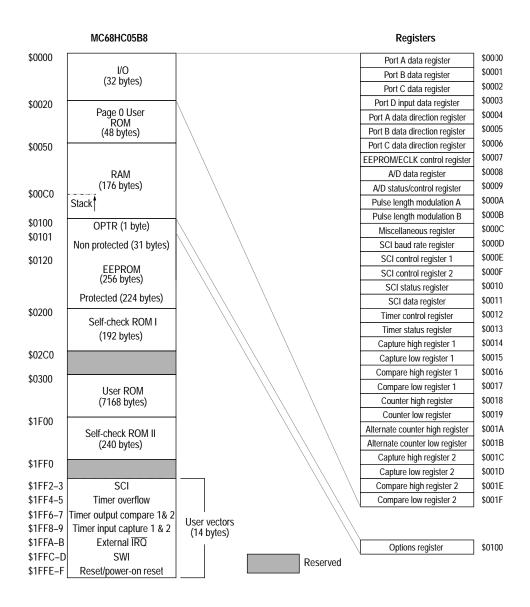

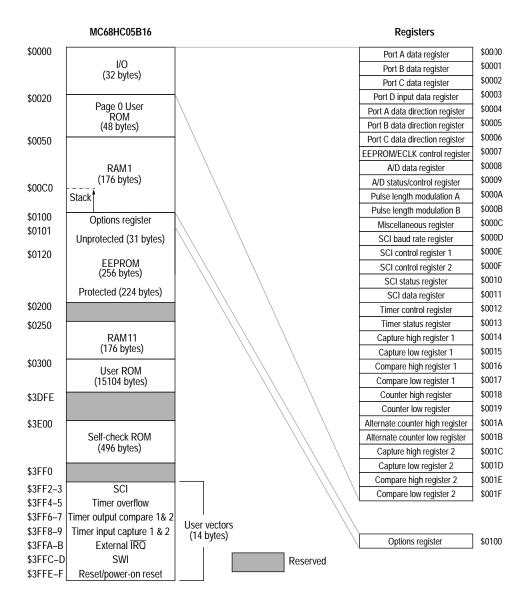

| 3-1              | Memory map of the MC68HC05B6                                   | 3–2            |

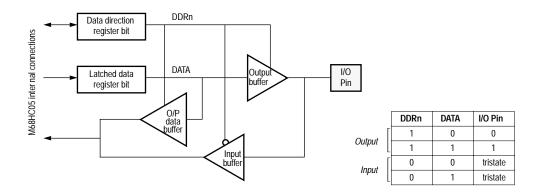

| 4-1              | Standard I/O port structure                                    | 4–2            |

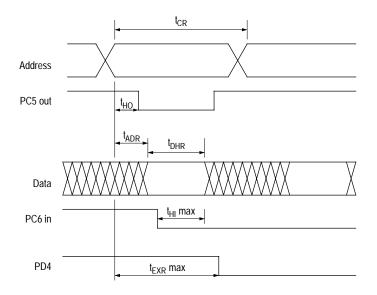

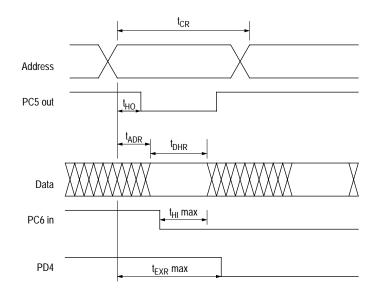

| 4-2              | ECLK timing diagram                                            | 4–3            |

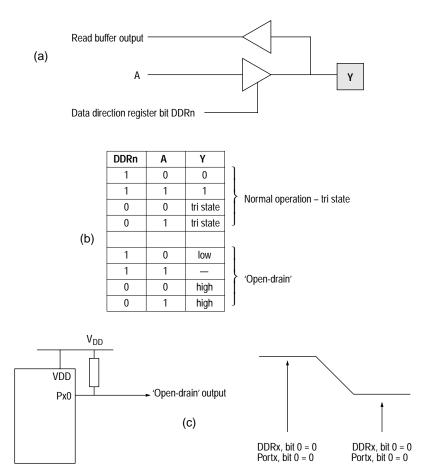

| 4-3              | Port logic levels                                              |                |

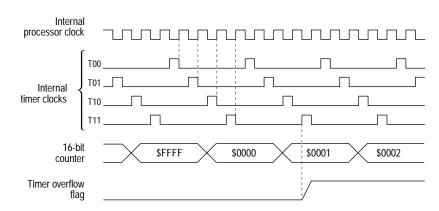

| 5-1              | 16-bit programmable timer block diagram                        | 5–2            |

| 5-2              | Timer state timing diagram for reset                           |                |

| 5-3              | Timer state timing diagram for input capture                   | 5–13           |

| 5-4              | Timer state timing diagram for output compare                  | 5–14           |

| 5-5              | Timer state timing diagram for timer overflow                  | 5–14           |

| 6-1              | Serial communications interface block diagram                  | 6–2            |

| 6-2              | SCI rate generator division                                    | 6–4            |

| 6-3              | Data format                                                    |                |

| 6-4              | SCI examples of start bit sampling technique                   |                |

| 6-5              | SCI sampling technique used on all bits                        | 6–7            |

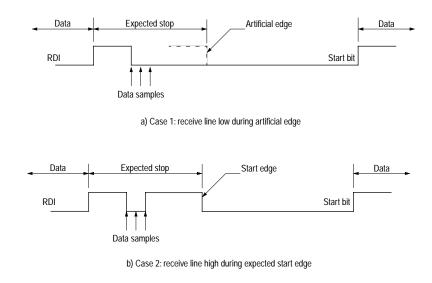

| 6-6              | Artificial start following a framing error                     |                |

| 6-7              | SCI start bit following a break                                |                |

| 6-8              | SCI example of synchronous and asynchronous transmission       |                |

| 6-9              | SCI data clock timing diagram (M=0)                            |                |

| 6-10             | SCI data clock timing diagram (M=1)                            |                |

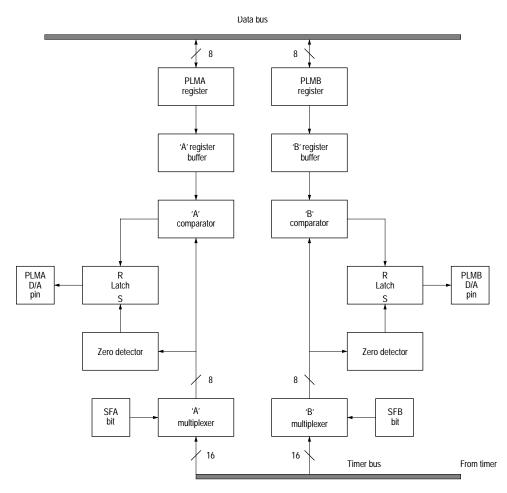

| 7-1              | PLM system block diagram                                       | 7–1            |

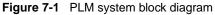

| 7-2              | PLM output waveform examples                                   |                |

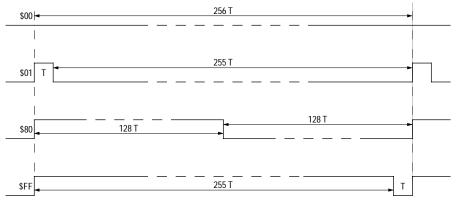

| 7-3              | PLM clock selection                                            |                |

| 8-1              | A/D converter block diagram                                    | 8–2            |

| 8-2              | Electrical model of an A/D input pin                           |                |

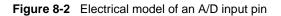

| 9-1              | Reset timing diagram                                           |                |

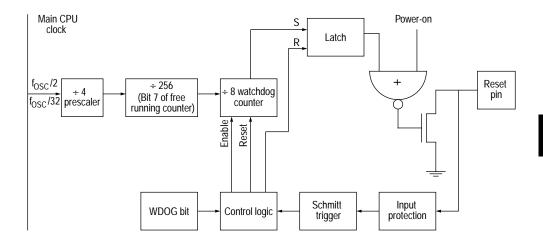

| 9-2              | Watchdog system block diagram                                  |                |

| 9-3              | Interrupt flow chart                                           | 9–8            |

| Figure |  |

|--------|--|

| Number |  |

| 40.4  |                                                                                    |

|-------|------------------------------------------------------------------------------------|

| 10-1  | Programming model                                                                  |

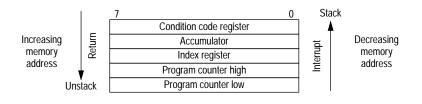

| 10-2  | Stacking order                                                                     |

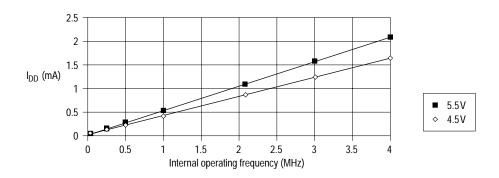

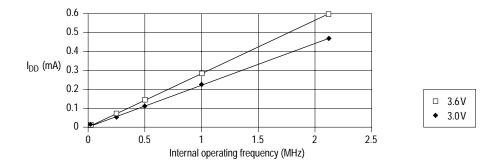

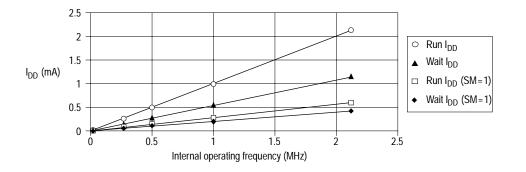

| 11-1  | Run I <sub>DD</sub> vs internal operating frequency (4.5V, 5.5V)                   |

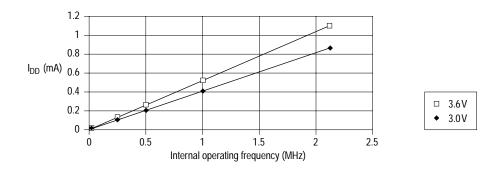

| 11-2  | Run $I_{DD}$ (SM = 1) vs internal operating frequency (4.5V, 5.5V)                 |

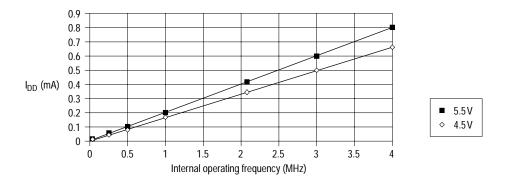

| 11-3  | Wait I <sub>DD</sub> vs internal operating frequency (4.5V, 5.5V)                  |

| 11-4  | Wait $I_{DD}$ (SM = 1) vs internal operating frequency (4.5V, 5.5V)                |

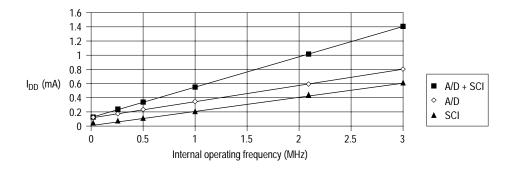

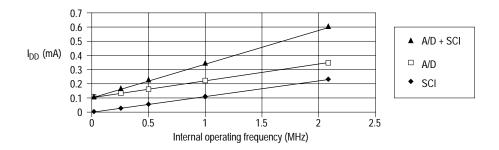

| 11-5  | Increase in $I_{DD}$ vs frequency for A/D, SCI systems active, VDD = 5.5V          |

| 11-6  | $I_{DD}$ vs mode vs internal operating frequency, $V_{DD}$ = 5.5V                  |

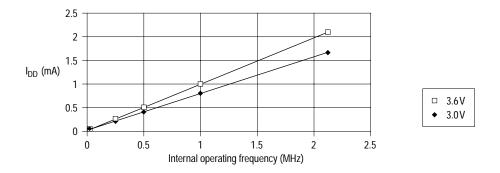

| 11-7  | Run I <sub>DD</sub> vs internal operating frequency (3 V, 3.6 V)                   |

| 11-8  | Run I <sub>DD</sub> (SM = 1) vs internal operating frequency (3V,3.6V)             |

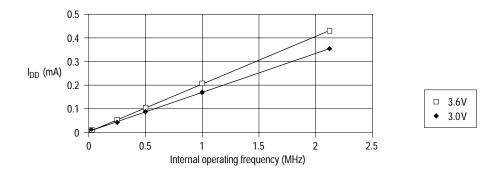

| 11-9  | Wait I <sub>DD</sub> vs internal operating frequency (3V, 3.6V)11–6                |

| 11-10 | Wait $I_{DD}$ (SM = 1) vs internal operating frequency (3V, 3.6V)                  |

| 11-11 | Increase in $I_{DD}$ vs frequency for A/D, SCI systems active, $V_{DD} = 3.6V11-7$ |

| 11-12 | $I_{DD}$ vs mode vs internal operating frequency, $V_{DD}$ = 3.6V                  |

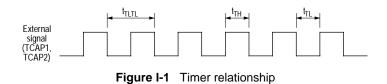

| 11-13 | Timer relationship11–12                                                            |

| 12-1  | 52-pin PLCC pinout for the MC68HC05B612-1                                          |

| 12-2  | 64-pin QFP pinout for the MC68HC05B612–2                                           |

| 12-3  | 56-pin SDIP pinout for the MC68HC05B612–3                                          |

| 12-4  | 52-pin PLCC mechanical dimensions 12-4                                             |

| 12-5  | 64-pin QFP mechanical dimensions12–5                                               |

| 12-6  | 56-pin SDIP mechanical dimensions12–6                                              |

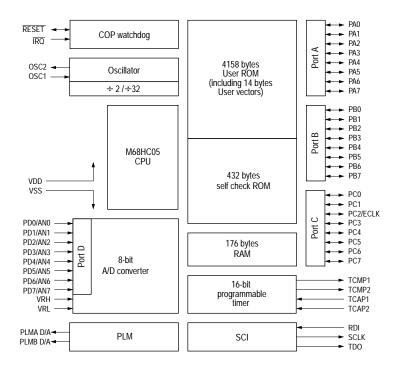

| A-1   | MC68HC05B4 block diagramA-2                                                        |

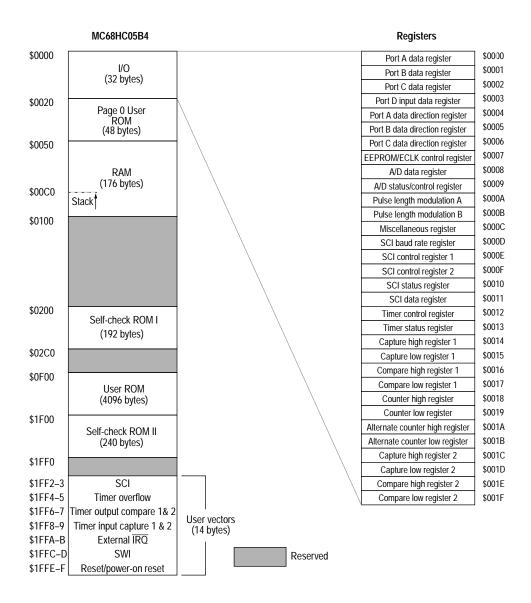

| A-2   | Memory map of the MC68HC05B4A-3                                                    |

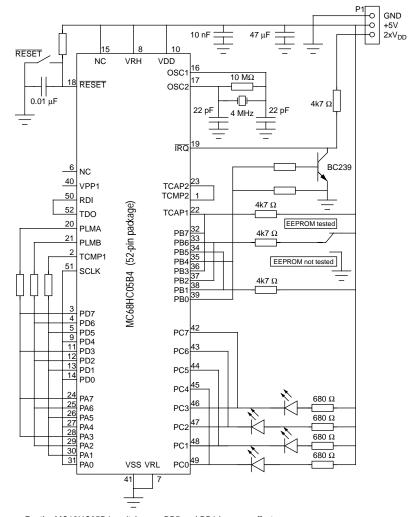

| A-3   | MC68HC05B4 self-check schematic diagramA–7                                         |

| B-1   | MC68HC05B8 block diagramB-2                                                        |

| B-2   | Memory map of the MC68HC05B8B-3                                                    |

| C-1   | MC68HC705B5 block diagram                                                          |

| C-2   | Memory map of the MC68HC705B5 C-3                                                  |

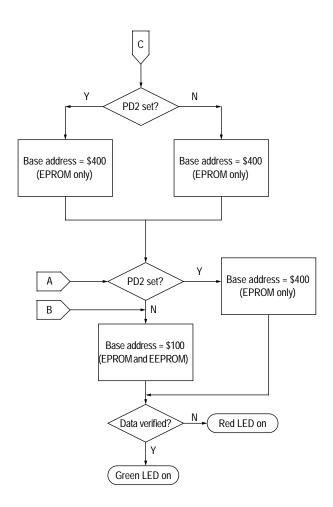

| C-3   | Modes of operation flow chart (1 of 2) C-9                                         |

| C-4   | Modes of operation flow chart (2 of 2)                                             |

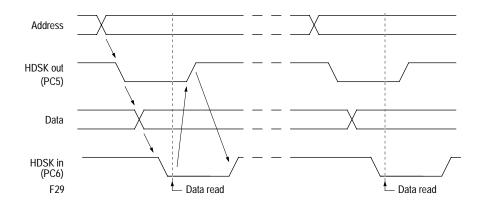

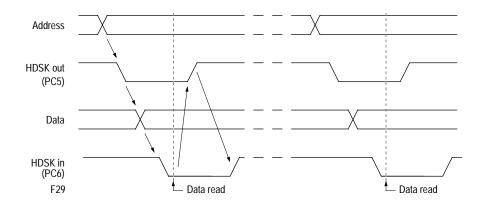

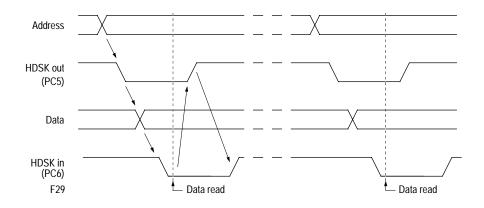

| C-5   | Timing diagram with handshakeC-11                                                  |

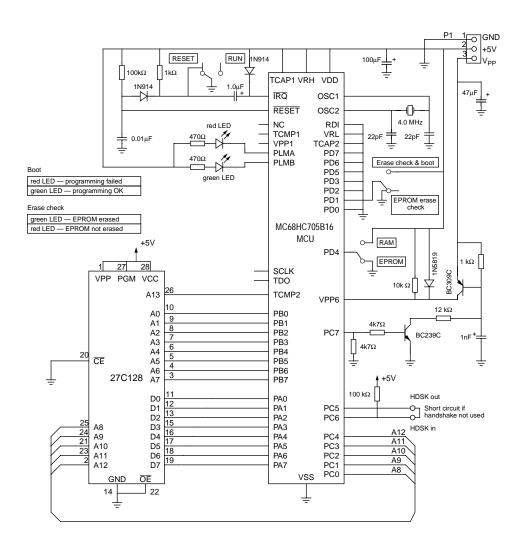

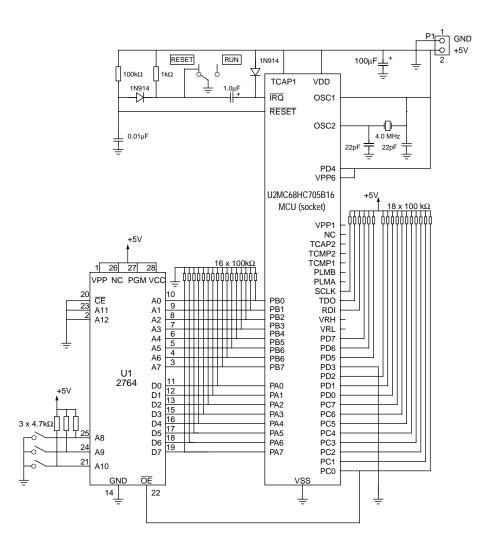

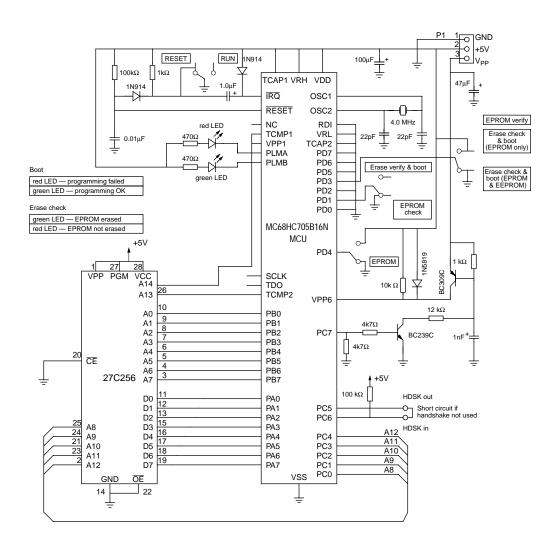

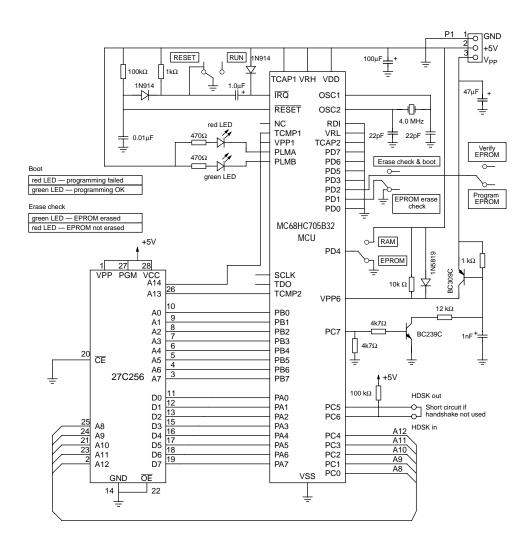

| C-6   | EPROM(RAM) parallel bootstrap schematic diagram                                    |

| C-7   | EPROM (RAM) serial bootstrap schematic diagram                                     |

| C-8   | RAM parallel bootstrap schematic diagram                                           |

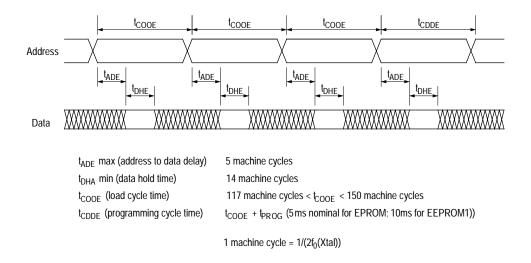

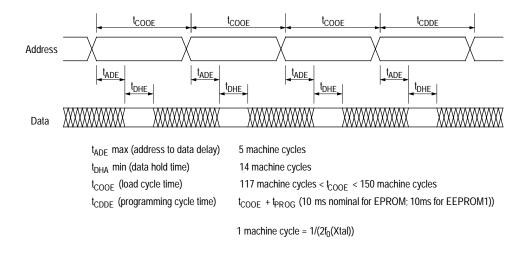

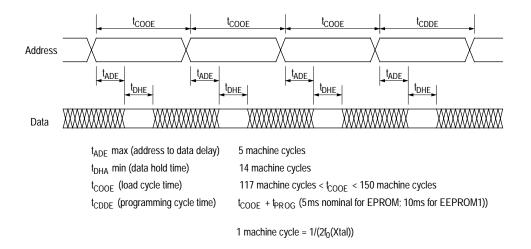

| C-9   | EPROM parallel bootstrap loader timing diagram                                     |

| C-10  | RAM parallel loader timing diagram                                                 |

| D-1   | MC68HC05B16 block diagram                                                          |

| D-2   | Oscillator connections                                                             |

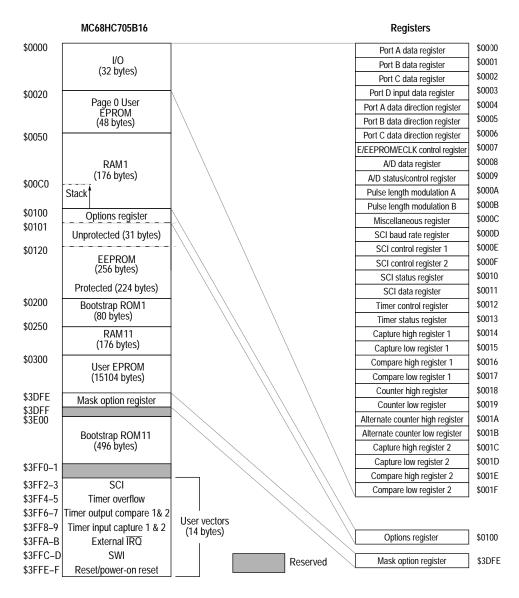

| D-3   | Memory map of the MC68HC05B16                                                      |

| E-1   | MC68HC705B16 block diagram                                                         |

| E-2   | Memory map of the MC68HC705B16                                                     |

| E-3   | Modes of operation flow chart (1 of 2)E–11                                         |

| 20    |                                                                                    |

| Figure<br>Number | TITLE                                               | Page<br>Number |

|------------------|-----------------------------------------------------|----------------|

| E-4              | Modes of operation flow chart (2 of 2)              | E–12           |

| E-5              | Timing diagram with handshake                       |                |

| E-6              | Parallel EPROM loader timing diagram                | E–14           |

| E-7              | EPROM Parallel bootstrap schematic diagram          | E–15           |

| E-8              | RAM/EPROM/EEPROM serial bootstrap schematic diagram | E–17           |

| E-9              | Parallel RAM loader timing diagram                  | E–19           |

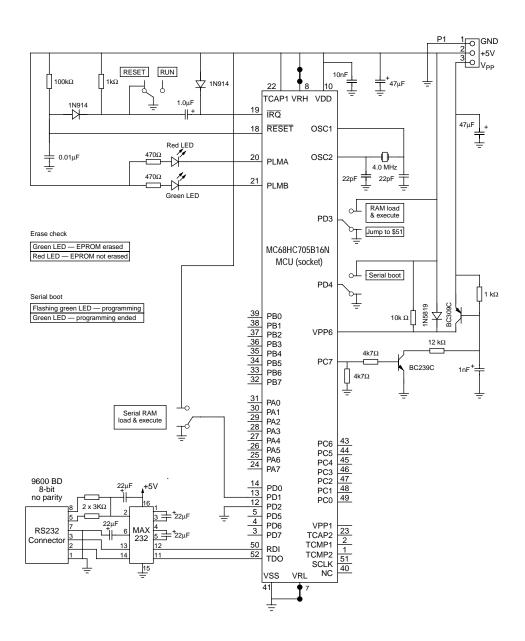

| E-10             | RAM parallel bootstrap schematic diagram            | E–20           |

| E-11             | Timer relationship                                  | E–28           |

| F-1              | MC68HC705B16N block diagram                         | F–2            |

| F-2              | Memory map of the MC68HC705B16N                     | F–3            |

| F-3              | Modes of operation flow chart (1 of 2)              |                |

| F-4              | Modes of operation flow chart (2 of 2)              |                |

| F-5              | Timing diagram with handshake                       |                |

| F-6              | Parallel EPROM loader timing diagram                |                |

| F-7              | EPROM parallel bootstrap schematic diagram          |                |

| F-8              | RAM load and execute schematic diagram              | .F–17          |

| F-9              | Parallel RAM loader timing diagram                  |                |

| F-10             | Timer relationship                                  | .F–26          |

| G-1              | MC68HC05B32 block diagram                           |                |

| G-2              | Memory map of the MC68HC05B32                       |                |

| H-1              | MC68HC705B32 block diagram                          |                |

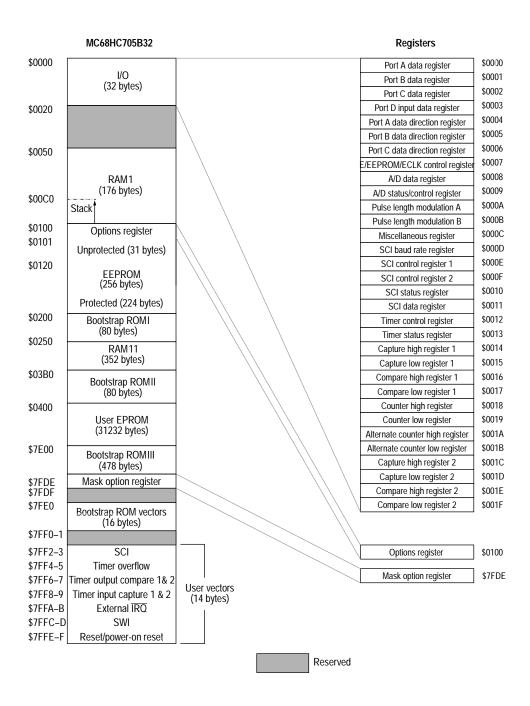

| H-2              | Memory map of the MC68HC705B32                      |                |

| H-3              | Modes of operation flow chart (1 of 2)              |                |

| H-4              | Modes of operation flow chart (2 of 2)              | H–15           |

| H-5              | Timing diagram with handshake                       |                |

| H-6              | Parallel EPROM loader timing diagram                |                |

| H-7              | EPROM parallel bootstrap schematic diagram          |                |

| H-8              | RAM load and execute schematic diagram              |                |

| H-9              | Parallel RAM loader timing diagram                  |                |

| H-10             | Timer relationship                                  |                |

| I-1              | Timer relationship                                  | I–5            |

THIS PAGE LEFT BLANK INTENTIONALLY

# **LIST OF TABLES**

| Table<br>Number | TITLE                                            | Page<br>Number |

|-----------------|--------------------------------------------------|----------------|

| 1-1             | Data sheet appendices                            | 1–1            |

| 2-1             | Mode of operation selection                      |                |

| 3-1             | EEPROM control bits description                  |                |

| 3-2             | Register outline                                 | 3–8            |

| 3-3             | IRQ sensitivity                                  |                |

| 4-1             | I/O pin states                                   | 4–2            |

| 6-1             | Method of receiver wake-up                       | 6–11           |

| 6-2             | SCI clock on SCLK pin                            | 6–13           |

| 6-3             | First prescaler stage                            | 6–18           |

| 6-4             | Second prescaler stage (transmitter)             | 6–18           |

| 6-5             | Second prescaler stage (receiver)                | 6–19           |

| 6-6             | SCI baud rate selection                          | 6–20           |

| 8-1             | A/D clock selection                              | 8–4            |

| 8-2             | A/D channel assignment                           |                |

| 9-1             | Effect of RESET, POR, STOP and WAIT              | 9–5            |

| 9-2             | Interrupt priorities                             | 9–7            |

| 9-3             | IRQ sensitivity                                  | 9–9            |

| 10-1            | MUL instruction                                  |                |

| 10-2            | Register/memory instructions                     | 10–5           |

| 10-3            | Branch instructions                              |                |

| 10-4            | Bit manipulation instructions                    |                |

| 10-5            | Read/modify/write instructions                   |                |

| 10-6            | Control instructions                             |                |

| 10-7            | Instruction set (1 of 2)                         |                |

| 10-8            | Instruction set (2 of 2)                         |                |

| 10-9            | M68HC05 opcode map                               |                |

| 11-1            | Absolute maximum ratings                         |                |

| 11-2            | DC electrical characteristics for 5V operation   |                |

| 11-3            | DC electrical characteristics for 3.3V operation |                |

| 11-4            | A/D characteristics for 5V operation             |                |

| 11-5            | A/D characteristics for 3.3V operation           |                |

| 11-6            | Control timing for 5V operation                  |                |

| 11-7            | Control timing for 3.3V operation                | 11–11          |

| Table<br>Number | TITLE                                                                      | Page<br>Number |

|-----------------|----------------------------------------------------------------------------|----------------|

| 13-1            | MC order numbers                                                           | 13–1           |

| 13-2            | EPROMs for pattern generation                                              | 13–2           |

| A-1             | Mode of operation selection                                                | A–1            |

| A-2             | Register outline                                                           |                |

| A-3             | MC68HC05B4 self-check results                                              | A–6            |

| B-1             | Register outline                                                           |                |

| C-1             | Register outline                                                           |                |

| C-2             | Mode of operation selection                                                |                |

| C-3             | Bootstrap vector targets in RAM                                            |                |

| C-4             | Additional DC electrical characteristics for MC68HC705B5                   |                |

| C-5             | Additional control timing for MC68HC705B5                                  |                |

| D-1             | Mode of operation selection                                                |                |

| D-2             | Register outline                                                           |                |

| E-1             | Register outline                                                           |                |

| E-2             | EPROM control bits description                                             |                |

| E-3             | EEPROM control bits description                                            |                |

| E-4             | Mode of operation selection                                                |                |

| E-5             | Bootstrap vector targets in RAM                                            |                |

| E-6             | Absolute maximum ratings                                                   |                |

| E-7             | DC electrical characteristics for 5V operation                             |                |

| E-8             | DC electrical characteristics for 3.3V operation                           |                |

| E-9             | A/D characteristics for 5V operation                                       |                |

| E-10            | A/D characteristics for 3.3V operation                                     |                |

| E-11            | Control timing for 5V operation                                            |                |

| E-12            | Control timing for 3.3V operation                                          |                |

| E-13            | DC electrical characteristics for 5V operation                             |                |

| E-14            | Control timing for 5V operation                                            |                |

| E-15            | Control timing for 3.3V operation                                          |                |

| F-1             | Register outline                                                           |                |

| F-2             | EPROM control bits description                                             |                |

| F-3<br>F-4      | EEPROM control bits description                                            |                |

| F-4<br>F-5      | Mode of operation selection                                                |                |

| F-5<br>F-6      | Bootstrap vector targets in RAM                                            |                |

| F-0<br>F-7      | Absolute maximum ratings<br>DC electrical characteristics for 5V operation |                |

| F-7<br>F-8      | DC electrical characteristics for 3.3V operation                           |                |

| F-9             | A/D characteristics for 5V operation                                       |                |

| F-10            | A/D characteristics for 3.3V operation                                     |                |

| F-10<br>F-11    | Control timing for 5V operation                                            |                |

| F-11            | Control timing for 3.3V operation                                          |                |

| F-12<br>F-13    | DC electrical characteristics for 5V operation                             |                |

| F-14            | Control timing for 5V operation                                            |                |

| Table<br>Number | TITLE                                            | Page<br>Number |

|-----------------|--------------------------------------------------|----------------|

| F-15            | Control timing for 3.3V operation                | .F–26          |

| G-1             | Register outline                                 | G–4            |

| H-1             | Register outline                                 | H–6            |

| H-2             | EPROM control bits description                   | H–9            |

| H-3             | EEPROM control bits description                  | H–10           |

| H-4             | Mode of operation selection                      | H–13           |

| H-5             | Bootstrap vector targets in RAM                  | H–19           |

| H-6             | Absolute Maximum ratings                         | H–22           |

| H-7             | DC electrical characteristics for 5V operation   | H–23           |

| H-8             | DC electrical characteristics for 3.3V operation | H–24           |

| H-9             | A/D characteristics for 5V operation             | H–25           |

| H-10            | A/D characteristics for 3.3V operation           | H–26           |

| H-11            | Control timing for 5V operation                  | H–27           |

| H-12            | Control timing for operation at 3.3V             | H–28           |

| H-13            | DC electrical characteristics for 5V operation   | H–29           |

| H-14            | Control timing for 5V operation                  | H–29           |

| H-15            | Control timing for 3.3V operation                | H–29           |

| I-1             | Ordering information                             | I–1            |

| I-2             | DC electrical characteristics for 5V operation   | I–2            |

| I-3             | A/D characteristics for 5V operation             | I–3            |

THIS PAGE LEFT BLANK INTENTIONALLY

# 1 INTRODUCTION

The MC68HC05B6 microcomputer (MCU) is a member of Motorola's MC68HC05 family of low-cost single chip microcomputers. This 8-bit MCU contains an on-chip oscillator, CPU, RAM, ROM, EEPROM, A/D converter, pulse length modulated outputs, I/O, serial communications interface, programmable timer system and watchdog. The fully static design allows operation at frequencies down to dc to further reduce the already low power consumption to a few micro-amps.

This data sheet is structured such that devices similar to the MC68HC05B6 are described in a set of appendices (see Table 1-1).

| Device                                                                                                     | Appendix | Differences from MC68HC05B6                                                                                |

|------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------|

| MC68HC05B4                                                                                                 | A        | 4K bytes ROM; no EEPROM                                                                                    |

| MC68HC05B8                                                                                                 | В        | 7.25K bytes ROM                                                                                            |

| MC68HC705B5                                                                                                | С        | 6K bytes EPROM; self-check replaced by bootstrap<br>firmware; no EEPROM                                    |

| MC68HC05B16                                                                                                | D        | 16K bytes ROM; increased RAM and self-check ROM                                                            |

| MC68HC705B16                                                                                               | E        | 16K bytes EPROM; increased RAM; self-check replaced by bootstrap firmware; modified power-on reset routine |

| MC68HC705B16N                                                                                              | F        | 16K bytes EPROM; increased RAM; self-check replaced by bootstrap firmware; modified power-on reset routine |

| MC68HC05B32                                                                                                | G        | 32K bytes ROM; no page zero ROM; increased RAM                                                             |

| MC68HC705B32 H 32K bytes EPROM; no page zero ROM; increased self-check mode replaced by bootstrap firmware |          | 32K bytes EPROM; no page zero ROM; increased RAM; self-check mode replaced by bootstrap firmware           |

| Table 1-1 | Data sheet | appendices |

|-----------|------------|------------|

|           | Dulu onool | apponatooo |

# 1.1 Features

#### Hardware features

- Fully static design featuring the industry standard M68HC05 family CPU core

- On chip crystal oscillator with divide by 2 or a software selectable divide by 32 option (SLOW mode)

- 2.1 MHz internal operating frequency at 5V; 1.0 MHz at 3V

- High speed version available

- 176 bytes of RAM

- 5936 bytes of user ROM plus 14 bytes of user vectors

- 256 bytes of byte erasable EEPROM with internal charge pump and security bit

- Write/erase protect bit for 224 of the 256 bytes EEPROM

- Self test/bootstrap mode

- Power saving STOP, WAIT and SLOW modes

- Three 8-bit parallel I/O ports and one 8-bit input-only port

- Software option available to output the internal E-clock to port pin PC2

- 16-bit timer with 2 input captures and 2 output compares

- Computer operating properly (COP) watchdog timer

- Serial communications interface system (SCI) with independent transmitter/receiver baud rate selection; receiver wake-up function for use in multi-receiver systems

- 8 channel A/D converter

- 2 pulse length modulation systems which can be used as D/A converters

- One interrupt request input plus 4 on-board hardware interrupt sources

- Available in 52-pin plastic leaded chip carrier (PLCC), 64-pin quad flat pack (QFP) and 56-pin shrink dual in line (SDIP) packages

- Complete development system support available using the MMDS05 development station with the M68HC05B32EM emulation module

- Extended operating temperature range of -40 to +125 °C

# 1.2 Mask options for the MC68HC05B6

The MC68HC05B6 has three mask options that are programmed during manufacture and must be specified on the order form.

- Power-on-reset delay (t<sub>PORL</sub>) = 16 or 4064 cycles

- Automatic watchdog enable/disable following a power-on or external reset

- Watchdog enable/disable during WAIT mode

- Warning: It is recommended that an external clock is always used if t<sub>PORL</sub> is set to 16 cycles. This will prevent any problems arising with oscillator stability when the device is put into STOP mode.

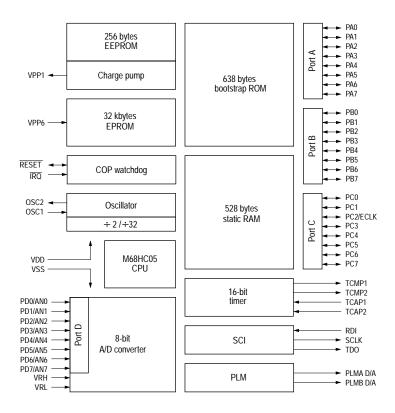

Figure 1-1 MC68HC05B6 block diagram

1

THIS PAGE LEFT BLANK INTENTIONALLY

# **2** MODES OF OPERATION AND PIN DESCRIPTIONS

# 2.1 Modes of operation

The MC68HC05B6 MCU has two modes of operation, namely single chip and self check modes. Table 2-1 shows the conditions required to enter each mode on the rising edge of RESET.

| IRQ pin              | TCAP1 pin            | PD3 | PD4 | Mode                |

|----------------------|----------------------|-----|-----|---------------------|

| $V_{SS}$ to $V_{DD}$ | $V_{SS}$ to $V_{DD}$ | Х   | Х   | Single chip         |

| 2V <sub>DD</sub>     | V <sub>DD</sub>      | 1   | 0   | Serial RAM loader   |

| 2V <sub>DD</sub>     | V <sub>DD</sub>      | 1   | 1   | Jump to any address |

# 2.1.1 Single chip mode

This is the normal operating mode of the MC68HC05B6. In this mode the device functions as a self-contained microcomputer (MCU) with all on-board peripherals, including the three 8-bit I/O ports and the 8-bit input-only port, available to the user. All address and data activity occurs within the MCU.

# 2.2 Serial RAM loader

The 'load program in RAM and execute' mode is entered if the following conditions are satisfied when the reset pin is released to  $V_{DD}$ . The format used is identical to the format used for the MC68HC805C4. The SEC bit in the options register must be inactive, i.e. set to '1'.

- IRQ at 2xV<sub>DD</sub>

- TCAP1 at V<sub>DD</sub>

- PD3 at V<sub>DD</sub> for at least 30 machine cycles after reset

- PD4 at V<sub>SS</sub> for at least 30 machine cycles after reset

In the 'load program in RAM and execute' routine, user programs are loaded into MCU RAM via the SCI port and then executed. Data is loaded sequentially, starting at RAM location \$0050, until the last byte is loaded. Program control is then transferred to the RAM program starting at location \$0051. The first byte loaded is the count of the total number of bytes in the program plus the count byte. The program starts at the second byte in RAM. During the firmware initialization stage, the SCI is configured for the NRZ data format (idle line, start bit, eight data bits and stop bit). The baud rate is 9600 with a 4 MHz crystal. A program to convert ASCII S-records to the format required by the RAM loader is available from Motorola.

If immediate execution is not desired after loading the RAM program, it is possible to hold off execution. This is accomplished by setting the byte count to a value that is greater than the overall length of the loaded data. When the last byte is loaded, the firmware will halt operation expecting additional data to arrive. At this point, the reset switch is placed in the reset position which will reset the MCU, but keep the RAM program intact. All routines can now be entered from this state, including the one which will execute the program in RAM (see Section 2.3).

To load a program in the EEPROM, the 'load program in RAM and execute' function is also used. In this instance the process involves two distinct steps. Firstly, the RAM is loaded with a program which will control the loading of the EEPROM, and when the RAM contents are executed, the MCU is instructed to load the EEPROM.

The erased state of the EEPROM is \$FF.

Figure 2-1 shows the schematic diagram of the circuit required for the serial RAM loader.

2

# 2.3 'Jump to any address'

The 'jump to any address' mode is entered when the reset pin is released to  $V_{DD}$ , if the following conditions are satisfied:

- IRQ at 2xV<sub>DD</sub>

- TCAP1 at V<sub>DD</sub>

- PD3 at V<sub>DD</sub> for at least 30 machine cycles after reset

- PD4 at V<sub>DD</sub> for at least 30 machine cycles after reset

This function allows execution of programs previously loaded in RAM or EEPROM using the methods outlined in Section 2.2.